AMD ha annunciato il primo chip a 2 nanometri, prodotto da TSMC. Si tratta del CCD (Core Complex Die) del processore EPYC di sesta generazione (nome in codice Venice) che arriverà sul mercato nel 2026. L’azienda di Santa Clara ha quindi anticipato Apple che dovrebbe utilizzare ancora il processo a 3 nanometri per i futuri chip M5 e A19.

AMD leader del mercato

I processori EPYC di sesta generazione sono basati sull’architettura Zen 6. La CPU avrà dunque CCD realizzati con tecnologia di processo N2 (2 nanometri) nelle fabbriche di TSMC. È il primo prodotto HPC (High Performance Computing) ad aver raggiunto il “tape-out”. La successiva validazione (superamento dei test) è avvenuta nella fabbrica di TSMC in Arizona (dove verranno aperti altri impianti nei prossimi quattro anni).

Lisa Su, Presidente e CEO di AMD, ha dichiarato:

TSMC è un partner chiave da molti anni e la nostra stretta collaborazione con i loro team di ricerca, sviluppo e produzione ha consentito ad AMD di fornire costantemente prodotti all’avanguardia che spingono i limiti dell’elaborazione ad alte prestazioni. Essere un cliente HPC leader per il processo N2 e per la Fab 21 di TSMC in Arizona sono ottimi esempi di come stiamo lavorando a stretto contatto per guidare l’innovazione e fornire le tecnologie avanzate che alimenteranno il futuro dell’informatica.

Questo è invece il commento di C.C. Wei, Presidente e CEO di TSMC:

Siamo orgogliosi di avere AMD come cliente leader nel settore HPC per la nostra avanzata tecnologia di processo a 2 nm (N2) e per la fabbrica di TSMC in Arizona. Stiamo promuovendo una significativa scalabilità tecnologica con conseguenti migliori prestazioni, efficienza energetica e rendimenti per il silicio ad alte prestazioni. Non vediamo l’ora di continuare a collaborare a stretto contatto con AMD per abilitare la prossima era dell’informatica.

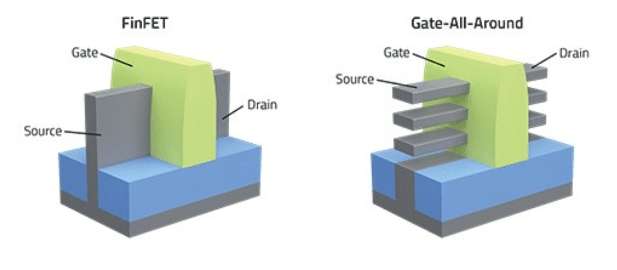

Fino al processo a 3 nanometri, TSMC ha utilizzato i FinFET (Fin Field Effect Transistor). Con il passaggio a 2 nanometri vengono usati i GAAFET (Gate All Around Field Effect Transitor) basati su nanofogli. Il termine “gate all around” indica che il gate circonda tutti i lati del canale (tra source e drain), come si può vedere nell’immagine.