La nuova architettura delle CPU AMD è ormai vicina al suo debutto e le informazioni, ufficiali o meno che siano, convergono tutte su un punto ben specifico. AMD definisce Bulldozer , nella sua massima espressione di CPU desktop (Zambezi), come un modello a 8-core . E non ci sarebbe nulla di strano se non fosse per via della sua particolare ed innovativa architettura costata al produttore già 8 rinvii ufficiali: a partire dal mese di agosto 2008 quando AMD parlava di Bulldozer a 45nm da lanciare sul mercato nel 2009, fino ad arrivare all’ultimo rinvio annunciato alla conferenza stampa tenuta in occasione del Computex 2011 a giugno.

Un percorso molto travagliato che ancora una volta ha caratterizzato lo sviluppo di una nuova architettura CPU per AMD e che ha portato a considerare un “core” come un’entità che non ha più vita a sé e che risulta essere incompleta se non affiancata ad un gemello. E come nel caso di gemelli siamesi, l’unità di base delle CPU Bulldozer è un modulo che ospita due core fisici affiancati e fusi assieme tanto che potremmo numerarli come “un core e mezzo”. Resta comunque ben inteso il fatto che una CPU Bulldozer a 8-core è in grado di gestire fino a 8 thread indipendenti. Ma lo stesso accade anche per un processore Sandy Bridge quad-core con Hyper Threading.

L’approccio di AMD è però decisamente diverso da quello di Intel. Quest’ultima parte da una classica architettura ove sono state aggiunte risorse nei moduli maggiormente richiesti per dare la possibilità di “sovraccaricare” ogni core che diventa così capace di gestire, nel caso migliore, 2 thread indipendenti. A Sunnyvale hanno invece fatto le cose al contrario partendo da due core fisici e togliendo alcune parti che possono essere messe in comune con l’intento di risparmiare transistor ed aumentare l’efficienza. Sparisce così il singolo core per lasciare il posto ad un “modulo Bulldozer” capace di gestire 2 thread ma non con la stessa potenza di due core fisici completi e indipendenti.

Approcci SMT e CMP. AMD sta nel mezzo

AMD si è collocata nel mezzo, fra l’approccio SMT della tecnologia Intel Hyper Threading, la quale fa leva sul fatto che molte parti della CPU sono spesso sottoutilizzate ma poi deve fare i conti con più thread che competono per la stessa risorsa, e fra l’approccio CMP in cui ogni core disponibile è dedicato ad uno ed un solo thread e gli evidenti sprechi di risorse sono giustificati dalla mancanza di problemi di concorrenza.

Per realizzare Bulldozer AMD ha studiato la situazione degli applicativi software attuali e verificato che le risorse di CPU vengono sfruttate appieno solo con operazioni su interi, decisamente meno con operazioni floating point. L’architettura che sta alla base delle future CPU prende spunto da tali osservazioni e le mette in pratica attraverso il blocco di base dual-core.

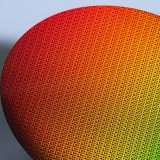

In un singolo Bulldozer module sono presenti due unità integer indipendenti dotate ognuna di uno scheduler, due unità di esecuzione e due unità di generazione degli indirizzi assieme ad una singola FPU condivisa. Quest’ultima è stata decisamente migliorata rispetto al passato tanto da essere in grado di prendersi cura di due thread attraverso un potenziato ed unico FPU scheduler e due FMAC (Fused Multiply-ACcumulate unit) a 128-bit. Il blocco “dual-core” risulta perciò efficiente quasi quanto due core indipendenti ma allo stesso tempo meno complesso e più parsimonioso dal punto di vista dei consumi.

Il modulo Bulldozer

Tutto questo ben si sposa con le estensioni AVX (Advanced Vector Extensions) che prevedono un file di registro SIMD ampio 256bit e che dovrebbero prendere il posto di quelle SSE. A differenza di queste ultime, quelle del set AVX utilizzano un formato a tre operandi nel quale il registro di destinazione è separato dai due registri sorgenti, permettendo la realizzazione di operazioni non distruttive. L’integrazione in Bulldozer di una singola FPU ha permesso di mettere assieme due FMAC a 128bit che, grazie alla tecnologia Flex FP , possono essere utilizzati in maniera molto flessibile: possono lavorare assieme su istruzioni a 256bit, nel qual caso sono in grado di produrre un singolo risultato per ogni ciclo di clock, oppure separatamente su istruzioni a 128bit producendo due risultati per ciclo di clock.

Teoricamente l’unità FPU di AMD dovrebbe raggiungere prestazioni molto elevate con applicazioni grafiche e multimediali. L’unità FMAC racchiude in una singola operazione una moltiplicazione ed una addizione, situazione molto frequente con gli applicativi appena citati. Invece di attendere due cicli di clock per portare a termine le due operazioni in maniera indipendente, il tutto può essere eseguito nella metà del tempo. In aggiunta, il risultato della moltiplicazione dato in pasto all’unità di add non subisce un arrotondamento come accadrebbe se le due unità fossero separate, offrendo una precisione superiore (è la stessa cosa che accade con le attuali GPU DirectX 11).

Infine, lo scheduler dedicato dell’unità FPU non va a concorrere con le operazioni sugli interi ed al contempo permette una più efficiente organizzazione delle istruzioni floating point, senza la necessità di attendere che sia libero lo scheduler delle unità integer.

Le CPU Intel Sandy Bridge annunciate lo scorso mese di gennaio prevedono un singolo scheduler per entrambe le unità ma dispongono di due unità vettoriali a 256bit in grado di produrre il risultato di una moltiplicazione a 256bit e quello di una addizione a 256bit. Tali operazioni sono però del tutto indipendenti, vista la mancanza di una unità FMAC (o meglio FMA). Intel integrerà unità di questo tipo solo nella futura architettura Haswell, prevista per il 2013.

In teoria le CPU AMD Bulldozer dovrebbero offrire prestazioni molto elevate. Ciò che conterà saranno però le reali prestazioni tanto in modalità single-thread che multithread. Suona molto strano il fatto che il produttore metta a confronto una CPU Bulldozer a 8-core con una CPU Sandy Bridge a 4-core. Il differente approccio resta solo un’arma commerciale o, nel migliore dei casi, la base per future evoluzioni, se poi con applicativi attuali di uso comune le prestazioni ottenute dal singolo modulo Bulldozer saranno le stesse offerte dal singolo core di una CPU Intel con Hyper Threading.

Le ultime indiscrezioni, che però è sempre bene prendere cum grano salis , parlerebbero di numeri interessanti per Bulldozer con applicazioni multi-threaded ma affiancati da valori meno confortanti, rispetto alle CPU rivali, con software single-threaded. L’impressione generale è che AMD voglia rimodellare le aspettative sul numero di core , un po’ come accaduto in passato con la corsa ai GHz. “Core” potrebbe indicare quel modulo capace di eseguire un thread indipendente oppure un modulo di differente concezione.

Core e threads

A cura di Dino Fratelli e Michele Carasia