Offrendo un importante scorcio sul futuro dei processori per PC, ieri Intel ha mostrato un prototipo di CPU contenente 48 core programmabili. Battezzata single-chip cloud computer (SCC), questa nuova CPU è l’ultimo frutto del programma di ricerca Tera-scale Computing di Intel, lo stesso che all’inizio del 2007 diede i natali a un prototipo di chip da 80 core , noto con il nome in codice Polaris .

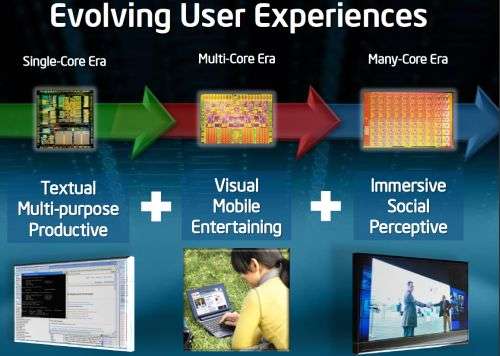

Intel afferma che processori con perfomance nell’ordine di grandezza di SCC apriranno la strada a computer dotati di una capacità visiva simile a quella degli esseri umani , in grado di tracciare oggetti e movimenti in tempo reale e con un’elevata accuratezza.

Intel afferma che processori con perfomance nell’ordine di grandezza di SCC apriranno la strada a computer dotati di una capacità visiva simile a quella degli esseri umani , in grado di tracciare oggetti e movimenti in tempo reale e con un’elevata accuratezza.

“Immaginiamo ad esempio di interagire un giorno con un computer per una lezione di danza virtuale o una sessione di shopping online in cui si utilizzano la videocamera 3D e il display di un notebook del futuro per riflettere un’immagine speculare di noi stessi, con indosso gli abiti che ci interessano. Sarà possibile rigirarsi e vedere l’effetto del tessuto e se il colore è appropriato per la nostra carnagione” spiega Intel in un comunicato. “Questo tipo di interazione potrebbe portare a eliminare la necessità di tastiere, telecomandi o joystick per i videogame. Secondo alcuni ricercatori, i computer potrebbero anche essere in grado di leggere le onde cerebrali, consentendo agli utenti di impartire i comandi, ad esempio dettare parole, semplicemente pensandoli, senza parlare”.

Intel Labs ha poi soprannominato il suo chip sperimentale single-chip cloud computer perché a suo dire ricorda l’organizzazione dei data center utilizzati per creare cloud di risorse informatiche tramite il Web.

“Con un chip come questo possiamo immaginare un cloud data center del futuro caratterizzato da un’efficienza energetica di gran lunga superiore rispetto alle attuali soluzioni, con un significativo risparmio di risorse in termini di spazio e costi energetici” ha aggiunto Justin Rattner, direttore di Intel Labs e CTO di Intel. “Nel corso del tempo prevediamo che questi concetti avanzati trovino una loro collocazione nei dispositivi mainstream, così come le tecnologie evolute del settore automobilistico, ad esempio il controllo elettronico del motore, gli airbag e i sistemi ABS, sono ormai disponibili in tutte le vetture”.

SCC rappresenta una significativa evoluzione tecnologica e concettuale di Polaris: la novità più importante è rappresentata dalla piena compatibilità con l’architettura x86 , e dunque con l’immenso bacino di software oggi disponibile per PC. Polaris si basava invece su un’architettura VLIW (Very Long Instruction Word), simile a quella utilizzata da Intel in Itanium. L’altra importante differenza tra i due chip è data dalla tecnologia di processo: 65 nanometri per Polaris, 45 nanometri per SCC .

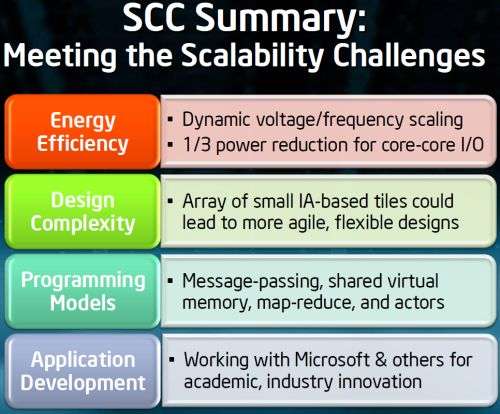

Il nuovo chippone ha una dimensione di 567 millimetri quadrati ed è costituito da 1,3 miliardi di transistor . Il suo consumo energetico va da 25 watt in stato di riposo a 125 watt a pieno carico : un consumo massimo paragonabile a quello dei più veloci processori server multi-core oggi sul mercato. Un livello di assorbimento energetico così contenuto è spiegabile con il fatto che i core di SCC sono molto più semplici rispetto a quelli di una CPU Core o Xeon, e in qualche modo simili ad un Atom : ad esempio, sono privi del supporto all’esecuzione delle istruzioni fuori ordine e non implementano alcun controllo di coerenza della cache.

“Obiettivo a lungo termine della ricerca è aggiungere caratteristiche ampiamente scalabili ai futuri computer che favoriscano lo sviluppo di categorie interamente nuove di applicazioni software e interfacce uomo-macchina” afferma BigI. “Il prossimo anno l’azienda prevede di coinvolgere il settore e il mondo accademico distribuendo almeno 100 di questi chip sperimentali per la ricerca pratica nello sviluppo di nuove applicazioni software e nuovi modelli di programmazione”. Intel ci tiene poi a sottolineare come SCC, benché funzionante, sia da considerarsi esclusivamente una concept CPU : il suo compito non è quello di evolvere in un prodotto commerciale, ma di indicare la direzione verso cui la ricerca di Intel si sta muovendo, e consentire all’industria di prepararsi con anticipo ai cambiamenti futuri. HP e Yahoo, ad esempio, sono due tra i colossi del settore IT che hanno già iniziato il porting delle proprie applicazioni cloud verso l’architettura alla base di SCC.

Intel sostiene di voler approfondire “tutti gli aspetti necessari a pianificare e coordinare i diversi core di questo chip sperimentale per i futuri chip mainstream”. Il passaggio dalle attuali architetture multi-core alle future architetture many core non è banale: l’uso di un numero così elevato di unità di calcolo richiede compilatori sempre più sofisticati e ottimizzati per la parallelizzazione del codice. Ma a rendere questa transizione ancor più complicata sono i molti cambiamenti che Intel sta introducendo nella sua architettura Tera-scale. Processori come SCC, infatti, non si limitano a moltiplicare i core di calcolo: come si è già accennato, essi includono al loro interno componenti e tecnologie che mimano, miniaturizzandoli, i componenti e le tecnologie utilizzati nei datacenter e nelle reti di computer.

Al centro dell’architettura di SCC ci sono le cosiddette tile (mattonelle), unità di calcolo costituite da due core, dalle rispettive memorie cache L2, da un router dedicato allo smistamento dei dati e da un buffer di memoria. I tile sono collegati tra loro da una rete mesh 2D da 6×4 nodi con un’ampiezza di banda massima di 256 GB/s. L’interfaccia di memoria integrata include invece quattro controller DDR3 capaci di gestire un totale di 64 GB di RAM.

L’idea alla base dell’architettura di SCC è quella di organizzare i core e le relative risorse, come cache e interconnessioni, in modo tale da massimizzare la capacità di elaborazione parallela della CPU. Il tile design fornisce un livello di flessibilità molto superiore a quello delle odierne architetture multicore: ogni tile può infatti comportarsi come una CPU indipendente , elaborando i dati in modo autonomo e ritrasmettendoli direttamente ai core adiacenti.

“Le attività correlate possono essere eseguite in core contigui e i risultati possono essere trasferiti direttamente da un core al successivo come in una catena di montaggio, per massimizzare le prestazioni complessive” spiega Intel. “Il chip sperimentale include infatti una rete ad alta velocità tra i core per la condivisione efficiente di informazioni e dati. Questa tecnica rende possibile un miglioramento significativo delle prestazioni delle comunicazioni e dell’efficienza energetica rispetto all’attuale modello di data center, perché i pacchetti di dati devono spostarsi solo di pochi millimetri sul chip anziché di decine di metri verso un altro sistema informativo”.

La maggiore granularità offerta dall’architettura di SCC va anche a beneficio del risparmio energetico : via software è infatti possibile gestire la tensione e la velocità di clock di ogni singolo core, attivarlo o disattivarlo, e cambiarne i livelli di performance “con un adattamento continuo – dice Intel – finalizzato a consumare l’energia minima necessaria in un dato momento”.

SCC è stato progettato da un team di 40 ingeneri provenienti dai centri di ricerca Intel di Bangalore (India), Brunswick (Germania) e Hillsboro (Oregon, USA). Il laboratorio di Brunswick, parte di Intel Labs Europe , si è focalizzato soprattutto nella progettazione della rete di interconnessione tra i core. Il team tedesco, responsabile delle attività di validazione dell’intero chip, ha applicato una tecnologia proprietaria di emulazione di microprocessori che ha consentito al team internazionale di testare i progetti software e hardware prima dell’effettiva realizzazione del chip. “In questo modo – spiega Intel – è stato possibile dimezzare i tempi di progettazione e accelerare lo sviluppo di software”.

I dettagli sull’architettura del chip dovrebbero essere pubblicati in un documento che verrà presentato nel corso dell’ International Solid State Circuits Conference che si terrà il prossimo febbraio a San Francisco.

Alessandro Del Rosso