Samsung ha annunciato l’avvio della produzione dei chip a 3 nanometri. La vera novità non è tuttavia la dimensione dei transistor, ma il tipo di tecnologia utilizzata. Per la prima volta viene utilizzata la tecnologia GAAFET (Gate-All-Around FET) che nell’implementazione di Samsung assume il nome proprietario Multi-Bridge-Channel FET (MBCFET). I primi processori sono destinati al settore HPC a basso consumo, ma successivamente arriveranno anche sul mercato mobile.

Chip a 3 nanometri con MBCFET

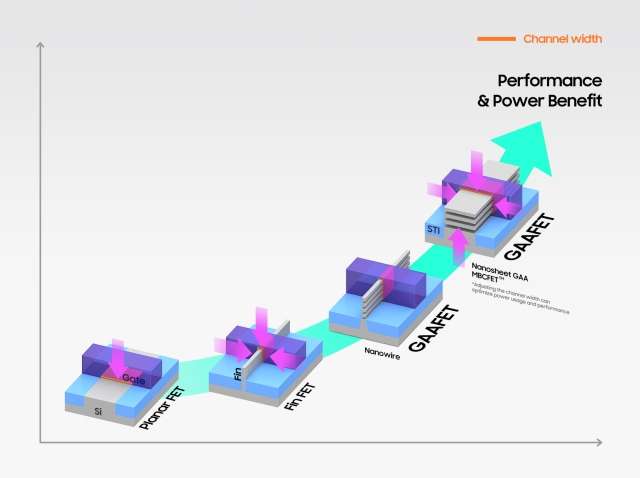

I transistor utilizzati in molti processori recenti sono basati sulla tecnologia FinFET. Si tratta di un tipo di transistor 3D, in cui il substrato di silicio forma una “pinna” e attraversa il gate che quindi copre il canale su tre lati. Questi transistor sono, ad esempio, utilizzati nel SoC Exynos 2200 a 4 nanometri dei Galaxy S22.

Per ridurre ulteriormente le dimensioni e incrementare le prestazioni è stata sviluppata la tecnologia GAAFET (Gate-All-Around FET), con la quale il gate circonda il canale su tutti i lati. L’implementazione standard prevede l’uso di “nanowire”. Quella di Samsung, denominata MBCFET, usa invece “nanosheet”. Cambiando la loro dimensione è possibile ottenere maggiori prestazioni (nanosheet più grandi) o minori consumi (nanosheet più piccoli).

Rispetto al processo a 5 nanometri, la prima generazione della tecnologia di Samsung può ridurre i consumi fino al 45% e incrementare le prestazioni fino al 23%, mentre con la seconda generazione del processo a 3 nanometri si otterrà una riduzione dei consumi fino al 50% e un aumento delle prestazioni fino al 30%.

L’annuncio dell’avvio della produzione conferma il vantaggio tecnologico di Samsung nei confronti della rivale TSMC che usa ancora transistor FinFET a 3 nanometri.