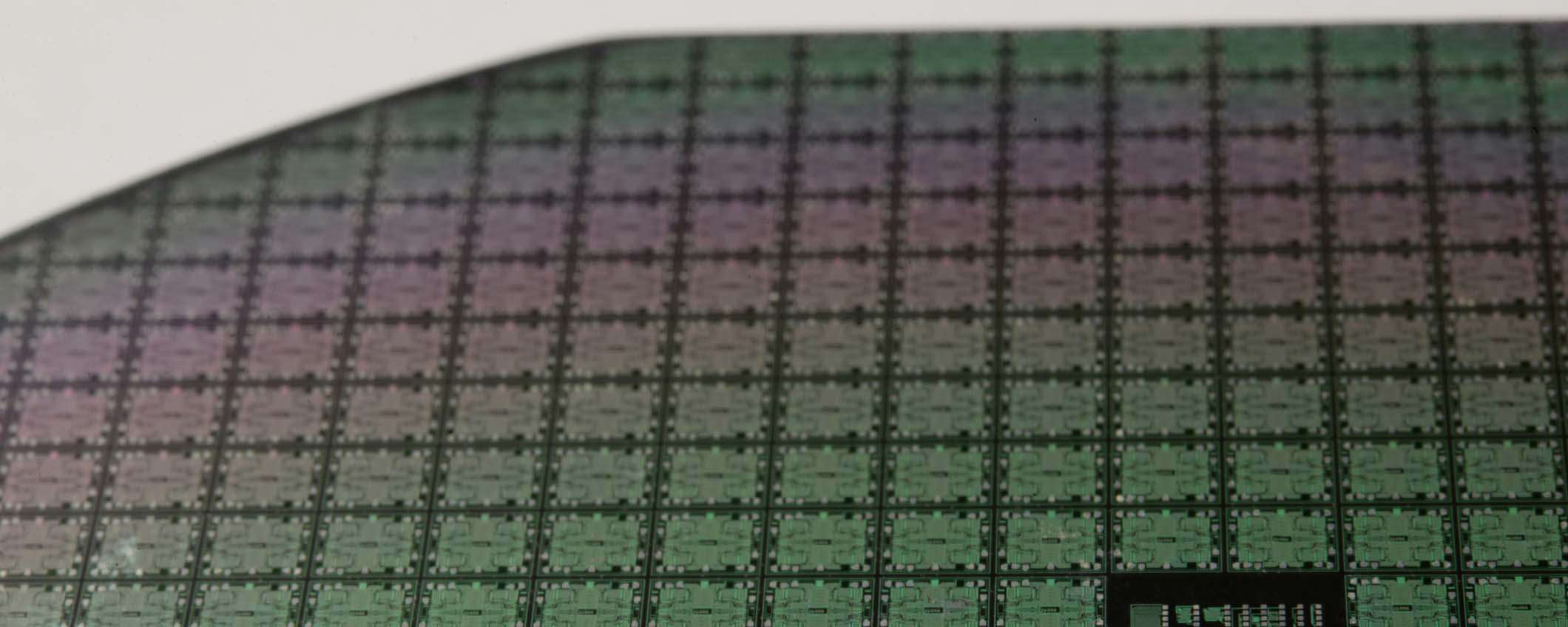

Dalle ultime indiscrezioni, sembra che TSMC abbia intenzione di abbandonare l’uso della litografia EUV ad alta apertura numerica (High-NA) per il suo prossimo nodo a 1.4nm, denominato A14, preferendo affidarsi alla più convenzionale tecnologia EUV a 0.33-NA che garantisce un maggior rapporto costo/efficienza.

TSMC non userà la tecnologia High-NA EUV per il prossimo nodo da 1.4 nanometri

TSMC ha rappresentato negli anni recenti l’avanguardia nell’adozione di nuove tecnologie per i semiconduttori, il che gli ha dato la possibilità di dettare la tendenza nel settore. Tuttavia, per il processo A14, l’azienda ha deciso di non impiegare gli strumenti di litografia più recenti e moderni, ovvero quelli con tecnologia High-NA EUV. La scelta è stata annunciata da Kevin Zhang, SVP della fonderia, durante il NA Technology Symposium, come riportato da Bits & Chips.

Nonostante ciò darebbe a Intel Foundry Services un vantaggio tecnologico, il motivo principale di questa decisione è rappresentato dal costo: l’adozione di strumenti con tecnologia High-NA EUV comporterebbe un aumento delle spese di produzione fino a 2,5 volte superiori rispetto ai metodi EUV più tradizionali, rendendo il nodo A14 significativamente più costoso e limitandone l’adozione ai prodotti consumer.

TSMC punta invece su schemi più avanzati e tecniche consolidate, come il multi-patterning con EUV a 0.33-NA, che consente di mantenere comunque un’elevata complessità nella progettazione, senza richiedere l’estrema precisione della tecnologia High-NA, permettendo così una produzione più economica. Un fattore che in particolare contribuisce all’aumento dei costi del High-NA è la necessità di utilizzare molteplici maschere per un singolo strato nella progettazione dei chip, il che incrementa le spese senza apportare benefici significativi. La fonderia taiwanese non esclude però l’uso del High-NA per futuri processi produttivi, come il nodo A14P previsto per il 2029.

Questa scelta pone tuttavia TSMC in ritardo rispetto a concorrenti come Intel Foundry, che prevede di adottare già il High-NA per il processo 18A nel 2026. Con un divario di almeno quattro anni nell’adozione di questa tecnologia, la fonderia taiwanese potrebbe cedere un vantaggio competitivo non di poco conto ai rivali, sebbene la sua strategia sembri orientata a bilanciare innovazione e sostenibilità economica.