Le principali aziende del settore, tra cui Intel, AMD, ARM, Samsung e TSMC, hanno annunciato la costituzione di un consorzio che stabilirà uno standard per l’interconnessione tra i chiplet. Sono state già ratificate le prime specifiche UCIe (Universal Chiplet Interconnect Express) basate su PCI Express e Compute Express Link. L’obiettivo è garantire l’interoperabilità e creare un ecosistema comune per il design dei processori.

UCIe 1.0: standard per i futuri SoC

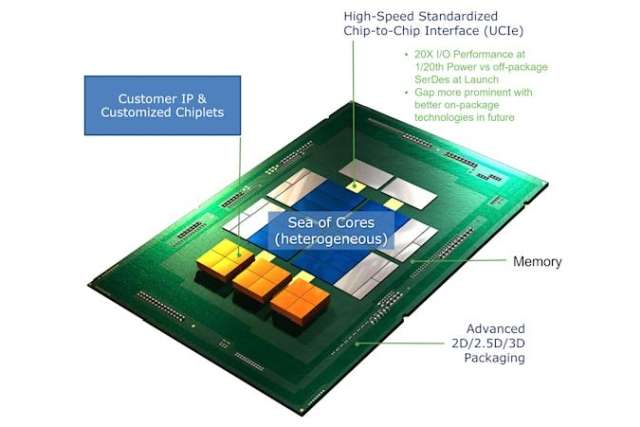

I chiplet sono utilizzati in molti SoC (System-on-Chip) moderni per ridurre i costi e realizzare le architetture eterogenee. Invece di progettare una CPU monolitica si creano singoli blocchi funzionali, chiamati chiplet, che sono combinati per ottenere il chip finale. È possibile ad esempio sfruttare CPU e GPU realizzate con differenti processi produttivi. Il consorzio UCIe vuole stabilire uno standard per il collegamento tra i singoli chiplet presenti sul package del SoC.

La prima versione delle specifiche è stata donata da Intel e copre due livelli (fisico e protocollo), ovvero come i singoli chiplet “parlano” tra loro attraverso le linee fisiche e gli standard PCI Express e Compute Express Link. Non viene invece indicata la tecnologia di packaging/bridging, in quanto UCIe è “agnostico”. È possibile utilizzare qualsiasi tecnologia (ad esempio EMIB o Foveros nel caso di Intel), garantendo comunque l’interoperabilità.

Grazie ad UCIe 1.0 sarà possibile creare SoC combinando i chiplet di diversi produttori. Le specifiche riguardano solo il packaging 2D e 2.5D. Quando sarà disponibile il packaging 3D, come Foveros Direct, lo standard verrà aggiornato. Queste sono le aziende che attualmente fanno parte del consorzio.